تقویت کننده سورس مشترک JFET از ترانزیستورهای اثر میدان پیوندی به عنوان دستگاه اکتیو اصلی خود، که ویژگیهای امپدانس ورودی بالا ارائه میدهد، استفاده میکنند.

مدارهای تقویت کننده ترانزیستوری مانند تقویت کننده امیتر مشترک با استفاده از ترانزیستورهای دو قطبی ساخته میشوند، اما میتوان تقویت کنندههای سیگنال کوچک را با استفاده از ترانزیستورهای اثر میدان نیز ساخت. این دستگاهها نسبت به ترانزیستورهای دو قطبی دارای این مزیت هستند که امپدانس ورودی آنها بسیار بالا و نویز خروجی آنها کم است و این باعث میشود که برای استفاده در مدارهای تقویت کننده که سیگنالهای ورودی بسیار کوچکی دارند، ایدهآل باشند.

طراحی مدار تقویت کننده مبتنی بر ترانزیستور اثر میدان پیوندی یا «JFET»، (در این آموزش کانال n)، یا حتی سیلیکون اکسید فلز یا «MOSFET»، دقیقا همان اصل مدار ترانزیستور دو قطبی مورد استفاده در مدار تقویت کننده کلاس A است که در آموزش قبلی بررسی کردیم.

در مرحله اول، یک نقطه کار یا «نقطه Q» مناسب برای بایاس درست مدار تقویت کننده JFET با پیکربندی تک تقویت کننده سورس مشترک (CS)، درین مشترک (CD) یا دنبال کننده سورس (SF) و گیت مشترک (CG) موجود برای اکثر دستگاههای FET باید پیدا شود.

این سه پیکربندی تقویت کننده JFET با پیکربندیهای امیتر مشترک، دنبال کننده امیتر و بیس مشترک در ترانزیستورهای دو قطبی مطابقت دارند. در این آموزش در مورد تقویت کنندههای FET، تقویت کننده JFET سورس مشترک محبوب را بررسی خواهیم کرد، چراکه پرکاربردترین طراحی تقویت کننده JFET است.

پیکربندی مدار تقویت کننده سورس مشترک JFET زیر را در نظر بگیرید.

تقویت کننده JFET سورس مشترک

1. تقویت کننده JFET سورس مشترک

1. تقویت کننده JFET سورس مشترک

مدار تقویت کننده از یک JFET کانال n تشکیل شده است، اما به جای آن میتوان از یک MOSFET حالت تخلیه کانال n نیز استفاده کرد، زیرا شماتیک مدار، به استثنای تغییر در FET، همان پیکربندی سورس مشترک خواهد بود. ولتاژ گیت JFET (VG) از طریق شبکه تقسیم ولتاژ تنظیم شده توسط مقاومتهای R۱ و R۲ و برای عملکرد در ناحیه اشباع آن بایاس شده است، که معادل ناحیه فعال ترانزیستور پیوند دو قطبی است.

برخلاف مدار ترانزیستور دو قطبی، تقریبا هیچ جریان ورودی از گیت FET پیوندی عبور نمیکند و میتوان آن را به عنوان مدار باز در نظر گرفت. بنابراین نیازی به منحنی مشخصه ورودی نیست. ما میتوانیم در جدول زیر JFET را با ترانزیستور پیوند دو قطبی (BJT) مقایسه کنیم.

مقایسه JFET با BJT

FET پیوندی | ترانزیستور دو قطبی |

گیت (G) | بیس (B) |

درین (D) | کلکتور (C) |

سورس (S) | امیتر (E) |

تغذیه گیت (VG) | تغذیه بیس (VB) |

تغذیه درین (VDD) | تغذیه کلکتور (VCC) |

جریان درین (ID) | جریان کلکتور (IC) |

از آنجا که JFET کانال n یک دستگاه حالت تخلیه و به طور معمول «روشن» است، برای تعدیل یا کنترل جریان درین، ولتاژ ورودی منفی نسبت به سورس مورد نیاز است. این ولتاژ منفی را میتوان با بایاس از طریق یک ولتاژ منبع تغذیه جداگانه یا با یک آرایش خود بایاس تامین کرد، به شرطی که حتی در صورت عدم وجود سیگنال ورودی، یک جریان ثابت از JFET عبور کند و VG بایاس معکوس پیوند pn گیت-سورس را حفظ کند.

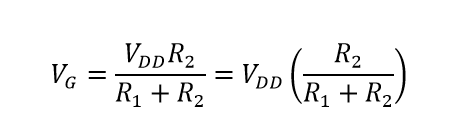

در مثال ساده ما، بایاس از طریق یک شبکه تقسیم ولتاژ تامین میشود که به ورودی اجازه میدهد تا با یک سیگنال سینوسی کاهش و افزایش ولتاژ در گیت ایجاد کند. هر جفت مقاومت مناسب با نسبت صحیح، ولتاژ بایاس درست را تولید میکند، بنابراین ولتاژ بایاس DC گیت (VG) به صورت زیر به دست میآید:

توجه داشته باشید که این معادله تنها نسبت مقاومتهای R۱ و R۲ را تعیین میکند، اما برای استفاده از امپدانس ورودی بسیار بالای JFET و همچنین کاهش اتلاف توان در مدار، باید این مقادیر مقاومت را تا حد ممکن بالا ببریم. مقادیری در محدوده 1MΩ تا 10MΩ رایج هستند.

سیگنال ورودی (Vin) تقویت کننده سورس مشترک JFET بین ترمینال گیت و ریل صفر ولت (0V) اعمال میشود. با اعمال یک مقدار ثابت ولتاژ گیت (VG)، JFET در «ناحیه اهمی» خود، مانند یک دستگاه مقاومت خطی، عمل میکند. مدار درین شامل مقاومت بار (RD) است. ولتاژ خروجی (Vout) در این مقاومت بار تولید میشود.

بازده تقویت کننده سورس مشترک JFET را میتوان با افزودن یک مقاومت (RS) به پایه سورس بهبود بخشید؛ همان جریان درین از این مقاومت عبور میکند. از مقاومت RS برای تنظیم «نقطه Q» تقویت کننده JFET نیز استفاده میشود.

هنگامی که JFET کاملاً «روشن» باشد، افت ولتاژی برابر با RS×ID در این مقاومت ایجاد میشود و پتانسیل ترمینال سورس را از 0V یا زمین، بالاتر میبرد. این افت ولتاژ در RS به دلیل جریان درین، شرایط بایاس معکوس لازم را در مقاومت گیت (R۲) فراهم کرده و عملا فیدبک منفی ایجاد میکند.

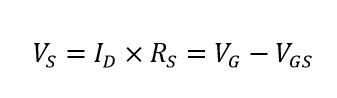

بنابراین برای اینکه بایاس معکوس پیوند گیت-سورس حفظ شود، ولتاژ سورس (VS) باید بالاتر از ولتاژ گیت (VG) باشد. بنابراین این ولتاژ سورس به شرح زیر به دست میآید:

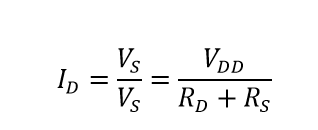

پس جریان درین (ID) همچنین برابر است با جریان سورس (IS)، چراکه «هیچ جریانی» وارد ترمینال گیت نمیشود و آن را میتوان به صورت زیر به دست آورد:

این مدار بایاس تقسیم ولتاژ، پایداری مدار تقویت کننده JFET سورس مشترک را هنگام تغذیه از یک منبع تغذیه منفرد، در مقایسه با مدار بایاس ولتاژ ثابت، بهبود میبخشد. هم مقاومت (RS) و هم خازن بای پس (CS) سورس اساسا عملکرد مشابه مقاومت و خازن امیتر را در مدار تقویت کننده ترانزیستور دو قطبی امیتر مشترک دارند، یعنی ایجاد پایداری خوب و جلوگیری از کاهش بهره ولتاژ. با این حال، قیمت پرداخت شده برای یک ولتاژ کار گیت تثبیت شده این است که ولتاژ منبع تغذیه بیشتر در RS کاهش مییابد.

مقدار خازن بای پس سورس به طور کلی زیاد، بالاتر از 100μF و قطبی است. این مقدار باعث میشود که امپدانس خازن بسیار کوچکتر، کمتر از 10% هدایت انتقالی (gm، ضریب انتقال نشان دهنده بهره) باشد. در فرکانسهای بالا، خازن بای پس اساسا به عنوان اتصال کوتاه عمل میکند و سورس مستقیما به زمین متصل شده است.

مدار و مشخصات اساسی تقویت کننده JFET سورس مشترک بسیار شبیه به تقویت کننده امیتر مشترک است. یک خط بار DC با اتصال دو نقطه مربوط به جریان درین (ID) و ولتاژ تغذیه (VDD) کشیده میشود، به یاد داشته باشید که وقتی ID=0: (VDD=VDS) و هنگامی که VDS=0: (ID=VDD/RL). بنابراین خط بار، تقاطع منحنیها در نقطه Q است.

منحنیهای مشخصه تقویت کننده JFET سورس مشترک

2. منحنی مشخصه تقویت کننده JFET سورس مشترک

2. منحنی مشخصه تقویت کننده JFET سورس مشترک

همانند مدار دو قطبی امیتر مشترک، خط بار DC برای تقویت کننده سورس مشترک JFET یک معادله خط مستقیم تولید میکند که شیب آن برابر است با -1/(RD+RS) و از محور عمودی ID در نقطه A برابر با VDD/(RD+RS) عبور میکند. انتهای دیگر خط بار از محور افقی در نقطه B عبور میکند که برابر است با ولتاژ تغذیه (VDD).

موقعیت واقعی نقطه Q روی خط بار DC به طور کلی در نقطه وسط خط بار قرار میگیرد (برای کلاس A) و با مقدار متوسط VG تعیین میشود که منفی است، زیرا JFET یک دستگاه حالت تخلیه است. مانند تقویت کننده دو قطبی امیتر مشترک، خروجی تقویت کننده JFET سورس مشترک ۱۸۰° با سیگنال ورودی اختلاف فاز دارد.

یکی از اصلی ترین معایب استفاده از JFET حالت تخلیه این است که باید بایاس معکوس داشته باشند. اگر این بایاس به هر دلیلی از کار بیافتد، ممکن است ولتاژ گیت-سورس افزایش یابد و مثبت شود و این خود باعث افزایش جریان درین و از کار افتادن ولتاژ درین (VD) میشود.

همچنین مقاومت بالای کانال (RDS(on)) FET پیوندی، همراه با جریان درین حالت پایدار در نقطه کار، باعث گرم شدن این دستگاهها میشود، بنابراین به هیت سینک اضافی نیاز است. با این حال، با استفاده از دستگاههای MOSFET حالت افزایشی، میتوان بیشتر مشکلات مربوط به استفاده از JFET را کاهش داد.

MOSFET ها، یا FET های اکسید فلز نیمه هادی، دارای امپدانس ورودی بسیار بیشتر و مقاومت کانال کمتری نسبت به JFET هستند. همچنین آرایش بایاس برای MOSFET متفاوت است، و هیچ جریانی از درین جریان نخواهد یافت، مگر آن که آنها را برای دستگاههای کانال n، به صورت مثبت و برای دستگاههای کانال p، به صورت منفی بایاس کنیم. در نتیجه یک ترانزیستور مطمئن داریم.

بهره توان و جریان تقویت کننده JFET

قبلا گفتیم که جریان ورودی (IG) یک تقویت کننده JFET سورس مشترک، به دلیل امپدانس گیت (RG) بسیار بالا، بسیار کوچک است. بنابراین یک تقویت کننده JFET سورس مشترک نسبت بسیار خوبی بین امپدانسهای ورودی و خروجی خود دارد و به ازای هر مقدار جریان خروجی (Iout)، تقویت کننده JFET دارای بهره جریان (Ai) بسیار بالا است.

به همین دلیل، تقویت کنندههای JFET سورس مشترک، به عنوان مدارهای تطبیق با امپدانس، بسیار با ارزش هستند و یا به عنوان تقویت کنندههای ولتاژ استفاده میشوند. به همین ترتیب، چون: توان = ولتاژ × جریان (P=V×I) و ولتاژهای خروجی معمولا چندین میلی ولت یا حتی چند ولت هستند، بهره توان (Ap) نیز بسیار زیاد است.

در مقاله بعدی بررسی خواهیم کرد که چگونه بایاس نادرست تقویت کننده ترانزیستوری باعث اعوجاج سیگنال خروجی به شکل اعوجاج دامنه به دلیل برش میشود و همچنین تاثیر اعوجاج فاز و فرکانس را بررسی خواهیم کرد.

دیدگاه خود را بنویسید