یک گیت منطقی دیجیتال، یک مدار الکترونیکی است که براساس ترکیب سیگنالهای موجود در ورودیهای خود؛ تصمیمات منطقی میگیرد.

گیتهای منطقی دیجیتال، میتوانند بیش از یک ورودی داشته باشند؛ برای مثال، ورودیهای A، B،C و D و… اما در حالت کلی، دارای یک خروجی دیجیتال (Q) خواهند بود. گیتهای منطقی منفرد، میتوانند به هم متصل یا کسکید شوند؛ تا یک تابع گیت منطقی با هر تعداد ورودی را شکل دهند یا مدارهای نوع ترتیبی و ترکیبی را بسازند و یا گیتهای منطقی متفاوتی را از گیتهای استاندارد تولید کنند.

گیتهای منطقی دیجیتال تجاری استانداردی که در دسترس میباشند؛ معمولا از دو خانواده یا نوع میباشند؛ نوع TTL که مخفف انگلیسی Transistor-Transistor Logic به معنای منطق ترانزیستور-ترانزیستور است و نمونهی آن سری ۷۴۰۰ میباشد و نیز نوع CMOS که مخفف Complementary Metal-Oxide-Silicon بوده و به معنای مکمل فلز-اکسید-سیلیکون است و تراشههای سری 4000 از نمونه های این نوع است. این نماد TTL یا CMOS به تکنولوژی منطقی مورداستفاده برای ساخت مدار مجتمع یا آیسی (IC) یا “تراشه (chip)” اشاره دارد.

بهطورکلی، ICهای منطقی TTL از ترانزیستورهای اتصال دوقطبی NPN و PNP ، و ICهای منطقی CMOS از ترانزیستورهای اثر میدانی نوع MOSFET یا JFET برای مدارهای ورودی و خروجی خود استفاده میکنند.

علاوهبر فناوری TTLو CMOS، گیتهای منطقی دیجیتال ساده نیز میتوانند با اتصال دیودها، ترانزیستورها و مقاومتها، برای تولید RTL، گیتهای منطقی مقاومت-ترانزیستور، DTL ، گیتهای منطقی دیود-ترانزیستور یا ECL و گیتهای منطقی امیتر-کوپلشده استفاده شوند؛ اما این نوع از گیتها، در مقایسه با خانواده محبوب CMOS کمتر، رایج هستند.

مدارهای مجتمع، که معمولا با نام IC خوانده میشوند؛ را میتوان باتوجه به تعداد ترانزیستورها یا “گیتهایی” که در آنها وجود دارد؛ به خانوادههای مختلف دستهبندی نمود. برای مثال، یک گیت سادهی AND تنها حاوی چند ترانزیستور است؛ درحالیکه، یک میکروپروسسور پیچیده، ممکن است؛ حاوی هزاران گیت ترانزیستور منفرد باشد. مدارهای مجتمع براساس تعداد گیتهای منطقی یا پیچیدگی مدارهای درون تراشه، طبقهبندی میشوند و طبقهبندی کلی برای تعداد گیتهای منفرد به شرح زیر است:

طبقهبندی مدارهای مجتمع

یکپارچهسازی در مقیاس کوچک یا (SSI)- حاوی حداکثر 10 ترانزیستور یا تعدادی گیت در یک پکیج تنها است؛ مانند گیتهای AND، OR و NOT.

یکپارچهسازی در مقیاس متوسط یا (MSI)- دارای ۱۰ تا ۱۰۰ ترانزیستور یا ۱۰ گیت در یک پکیج تنها است و عملیات منطقی در جمعکننده، دیکدر، شمارنده، فلیپ فلاپ و مالتیپلکسر را انجام میدهد.

یکپارچهسازی در مقیاس بزرگ یا (LSI)- دارای 100 تا 1000 ترانزیستور یا 100 گیت است و عملیات منطقی خاص در تراشههای I/O، حافظه، واحدهای حساب و منطقی انجام میدهد.

یکپارچهسازی در مقیاس خیلی بزرگ یا (VLSI)– دارای ۱۰۰۰ تا ۱۰۰۰۰ ترانزیستور یا ۱۰۰۰ گیت است و عملیات ترکیبی در پردازندهها، آرایههای حافظهی بزرگ و دستگاههای منطقی قابل برنامهریزی را انجام میدهد.

یکپارچهسازی در مقیاس خیلی خیلی بزرگ یا (SLSI)- دارای 10000 تا 100000 ترانزیستور در یک پکیج تنها است و عملیات ترکیبی در تراشههای میکروپروسسور، میکروکنترلر، PIC پایه و ماشین حساب را انجام میدهد.

یکپارچهسازی در مقیاس فوقالعاده بزرگ یا (ULSI)- بیش از 1 میلیون ترانزیستور- این واحدها در CPU رایانهها،GPU، پردازندههای ویدئویی، میکروکنترلرها، FPGAها و PICهای پیچیده استفاده میشود.

درحالیکه، طبقهبندی ULSI “مقیاس فوقالعاده بزرگ”، کمتر مورداستفاده قرار میگیرد؛ سطح دیگری از یکپارچهسازی که نشاندهندهی پیچیدگی مدار مجتمع است؛ با نام سیستم-برروی-تراشه یا (SOC) به اختصار، شناخته میشود. دراینجا، هر جز منحصربهفرد مانند ریزپردازنده، حافظه، تجهیزات جانبی، منطق I/O و… همگی برروی یک قطعه سیلیکون تولید میشوند و یک سیستم الکترونیکی کامل را در یک تراشهی واحد نشان میدهند و به معنای واقعی کلمه، “یکپارچهشده” در یک مدار مجتمع است.

این تراشههای یکپارچه کامل که میتوانند تا 100 میلیون گیت ترانزیستور سیلیکونی CMOS را در یک پکیج داشته باشند؛ معمولا در تلفنهای همراه، دوربینهای دیجیتال، میکروکنترلرها، PIC و اپلیکیشنهای نوع رباتیک استفاده میشوند.

قانون مور (Moore)

در سال 1965، گوردون مور، یکی از بنیانگذاران شرکت اینتل (Intel) باتوجه به توسعهی فناوری گیت ترانزیستور، پیشبینی کرد؛ که “تعداد ترانزیستورها و مقاومتهای روی یک تراشه در هر 18 ماه دوبرابر میشود.” در زمانی که او، در این سال، نظر معروف را بیان نمود؛ تقریبا تنها 60 گیت ترانزیستور روی تک تراشه یا قالب سیلیکونی وجود داشت.

اولین ریزپردازندهی (microprocessor) جهان در سال 1971، اینتل 4004 بود؛ که دارای گذرگاه دادهی 4 بیتی بوده و شامل 2300 ترانزیستور برروی یک تک تراشه بود و با 600 کیلوهرتز عمل میکرد. امروزه، شرکت اینتل، تعداد سرسامآور 1.2 میلیارد گیت ترانزیستور منحصربفرد را برروی تراشهی ریزپردازندهی 64 بیتی Quad-core i7-2700K Sandy Bridge جدید خود قرار داده که با تقریبا 4 گیگاهرتز کار میکند. تعداد ترانزیستورهای روی تراشهها، همچنان درحال افزایش است؛ زیرا ریزپردازندهها و میکروکنترلرها جدیدتر، با سرعت زیادی، ساخته میشوند.

وضعیتهای منطق دیجیتال

گیت منطقی دیجیتال، بلوک اصلی ساختمانی است؛ که تمام مدارهای الکترونیکی دیجیتال و سیستمهای مبتنی بر ریزپردازنده از آن ساخته میشوند. گیتهای منطقی دیجیتال پایه، عملیات منطقی OR، AND و NOT را روی اعداد باینری انجام میدهند.

در طراحی منطق دیجیتال، فقط دو سطح یا حالت ولتاژی مجاز است و به این حالتها، درحالت کلی، منطق “1” و منطق “0” یا HIGH و LOW یا TRUE و FALSE گفته میشود. این دوحالت، در جبر بولی و جداول درستی استاندارد به ترتیب با ارقام باینری “1” و “0” نشان داده میشوند.

یک مثال خوب از حالت (وضعیت) دیجیتال، یک کلید روشنایی ساده است. سوئیچ میتواند، در یک حالت یا حالت دیگر، “روشن (ON)” یا “خاموش (OFF)” باشد؛ اما این امر، نمیتواند همزمان اتفاق بیفتد. پس میتوانیم رابطهی بین این حالتهای دیجیتال مختلف را بهصورت زیر خلاصه کنیم:

جبر بولی

منطق بولی

وضعیت ولتاژ

منطق "۱" | صحیح ((T) TRUE) | بالا ((H) HIGH) |

منطق "۰" | غلط ((F) FALSE) | پایین ((L) LOW) |

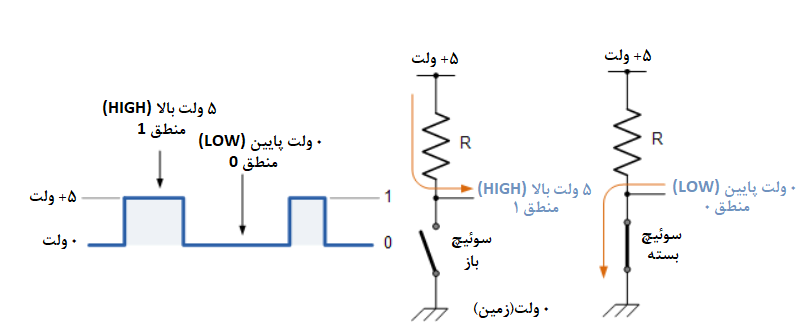

بیشتر گیتها یا سیستمهای منطقی دیجیتال، از “منطق مثبت” استفاده میکنند؛ که در آن سطح منطقی “0” یا “LOW” با ولتاژ صفر،0 ولت یا زمین و سطح منطقی “1” یا “HIGH” با ولتاژ بالاتر مانند +5 ولت، با تغییر از یک سطح ولتاژ به دیگری، از یک سطح منطقی “0” به “1” یا “1” به “0”، در سریعترین زمان ممکن و با جلوگیری از هرگونه عملکرد معیوب مدار منطقی ساخته میشود.

همچنین یک سیستم مکمل “منطق منفی” نیز وجود دارد؛ که در آن مقادیر و قوانین منطق “۰” و “۱” معکوس میشوند؛ اما در این بخش آموزشی، در مورد گیتهای منطقی دیجیتال، ما فقط به قرارداد منطق مثبت که رایجترین نوع مورد استفاده است، اشاره خواهیم داشت.

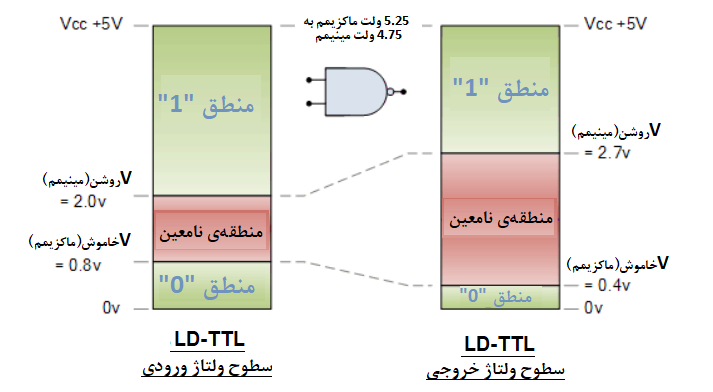

در آیسیهای استاندارد TTL (منطق ترانزیستور-ترانزیستور)، یک محدودهی ولتاژ از پیش تعریفشده برای سطوح ولتاژ ورودی و خروجی وجود دارد؛ که دقیقا سطح منطقی “1” و سطح منطقی “0” را مشخص میکند؛ که در زیر نشان داده شدهاست.

سطوح ولتاژ ورودی و خروجی TTL

انواع گیتهای منطقی در هر دو خانوادهی دو قطبی 7400 و CMOS 4000 گیتهای منطقی دیجیتال مانند 74Lxx، 74LSxx،74HCxx، 74HCTxx، 74ACTxx و … وجود دارند؛ که هرکدام دارای مزایا و معایب خاص خود در مقایسه با دیگری میباشند. ولتاژ سوئیچینگ دقیق موردنیاز برای تولید منطق “0” یا منطق “1” به گروه یا خانوادهی منطقی خاصی بستگی دارد.

با این حال، هنگام استفاده از منبع تغذیهی استاندارد +5 ولت؛ هر ورودی ولتاژ TTL بین 2 ولت و 5 ولت، بهعنوان منطق “1” یا “HIGH” درنظر گرفته میشود؛ درحالیکه، هر ورودی ولتاژ زیر 0.8 ولت بهعنوان منطق “0” یا “LOW” شناخته میشود. ناحیهی ولتاژ بین این دو سطح ولتاژ چه بهعنوان ورودی و چه بهعنوان خروجی، منطقهی نامعین نامیده میشود و عملکرد در این ناحیه ممکن است؛ باعث شود که گیت منطقی، خروجی کاذب تولید کند.

خانوادهی منطقی CMOS 4000 از سطوح مختلفی از ولتاژ، در مقایسه با انواع TTL استفاده میکند؛ زیرا با استفاده از ترانزیستورهای اثر میدانی یا FET طراحی شدهاند. در فناوری CMOS، یک سطح منطقی “1”، بین 3 تا 18 ولت و سطح منطقی “0”، زیر 1.5 ولت است. پس جدول زیر تفاوت بین سطوح منطقی گیتهای منطقی مرسوم TTL و CMOS را نشان میدهد.

سطوح منطق TTL و CMOS

نوع

منطق ۰

منطق ۱

TTL | ۰ تا ۰.۸ ولت | 2 تا 5 ولت (VCC) |

CMOS | ۰ تا ۱.۵ ولت | 3 تا 1.7 ولت (VDD) |

پس باتوجه به مشاهدات فوق، میتوانیم گیت منطقی دیجیتال TTL ایدهآل را بهعنوان گیتی تعریف کنیم؛ که دارای سطح منطقی “LOW”، “0” از 0 ولت (زمین) و سطح منطقی HIGH””، “1” از +5 ولت است و بهصورت زیر میتوان آن را نشان داد:

سطوح ولتاژ گیت منطقی دیجیتال TTL ایدهآل

جایی که باز یا بستهشدن سوئیچ، یک سطح منطقی “1” یا یک سطح منطقی “0” ایجاد میکند؛ که مقاومت R بهعنوان مقاومت pull-up”( پول آپ)” شناخته میشود.

نویز منطق دیجیتال

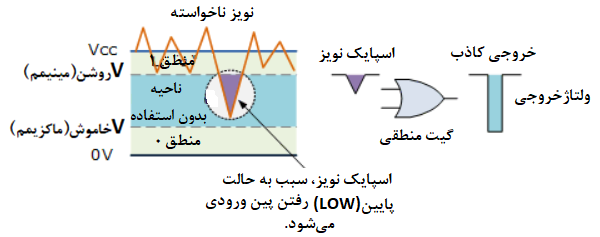

با این وجود، بین این مقادیر تعریفشدهی HIGH و LOW، چیزی قرار دارد؛ که بهطورکلی، زمین غیرانسانی (no-man’s land)، نامیده میشود ( ناحیه آبی رنگ بالا) و اگر مقداری از ولتاژ سیگنال را در این منطقهی زمین غیرانسانی اعمال کنیم؛ نمیدانیم که آیا گیت منطقی در آن، بهصورت سطح منطق “0” یا سطح منطق”1″ پاسخ میدهد و خروجی غیرقابل پیشبینی خواهد بود.

نویز نام دادهشده به ولتاژ تصادفی و ناخواستهای است؛ که توسط تداخل خارجی به مدارهای الکترونیکی القا میشود، مانند سوئیچهای مجاور، نوسانات منبع تغذیه یا سیمها و سایر رساناهایی که تشعشعات الکترومغناطیسی سرگردان را میگیرند. پس برای اینکه یک گیت منطقی تحت تاثیر نویز قرار نگیرد، باید دارای مقدار معینی حاشیه نویز یا مصونیت نویز باشد.

مصونیت نویز گیت منطقی دیجیتال

در مثال بالا، سیگنال نویز بر روی ولتاژ منبع تغذیهی VCC قرار میگیرد و تا زمانیکه بالاتر از سطح حداقل (Vروشن(مینیمم)) باشد؛ ورودی و خروجی مربوط به گیت منطقی تحت تاثیر قرار نمیگیرند. اما هنگامیکه، سطح نویز به اندازهی کافی بزرگ میشود و یک اسپایک نویز باعث میشود؛ سطح ولتاژ HIGH به زیر این حداقل کاهش یابد؛ گیت منطقی ممکن است؛ این اسپایک را بهعنوان ورودی سطح LOW تعبیر کند و خروجی را تغییر دهد و بر این اساس یک سوئچینگ خروجی کاذب ایجاد کند.

گیتهای منطقی دیجیتال پایهی ساده

گیتهای منطقی دیجیتال ساده را میتوان با ترکیب ترانزیستورها، دیودها و مقاومتها، با یک مثال ساده از یک گیت دیود-مقاومت منطقی (DRL) AND و یک گیت منطقی دیود- ترانزیستور (DTL)NAND که در زیر آورده شدهاست؛ ساخت.

مدار دیود - ترانزیستور

مدار دیود - مقاومت

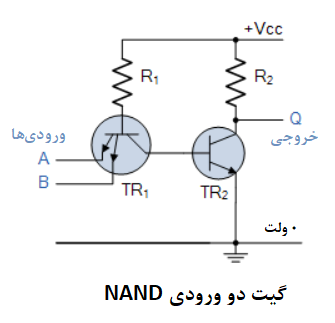

گیت دو ورودی NAND

گیت دو ورودی AND

یک گیت AND دیود-ترانزیستور ساده دو ورودی را میتوان با افزودن یک مرحله تکی ترانزیستور وارونساز (NOT) به یک گیت NAND تبدیل کرد. استفاده از قطعات گسسته مانند دیود، مقاومت و ترانزیستور برای ساخت مدارهای گیت منطقی دیجیتال در آیسیهای تجاری بهصورت عملی استفاده نمیشود؛ زیرا این مدارها دارای تاخیر انتشار یا تاخیر گیت و همچنین افت توان ناشی از مقاومتهای پول-آپ (Pull-up) هستند.

یکی دیگر از معایب منطق دیود-مقاومت، این است؛ که امکان Fan-out” (ظرفیت خروجی)” وجود ندارد؛ که توانایی یک خروجی واحد برای راهاندازی بسیاری از ورودیهای مراحل بعدی است. همچنین این نوع طراحی بهطور کامل “خاموش (OFF)” نمیشود؛ زیرا منطق “0”، ولتاژ خروجی 0.6 ولت (افت ولتاژ دیود) را تولید میکند و بنابراین، از طراحهای مدار TTL و CMOS زیر استفاده میشود.

گیتهای منطقی TTL پایه

گیت AND دیود_مقاومت سادهی بالا، از دیودهای جداگانه برای ورودیهای خود، بهصورت یک گیت برای هر ورودی استفاده میکند. از آنجاییکه، یک ترانزیستور دوقطبی، عملا دو اتصال دیودی متصل است؛ که نشاندهندهی یک قطعه NPN (منفی-مثبت-منفی) یا یک قطعهی PNP (مثبت-منفی-مثبت) است؛ دیودهای ورودی مدار منطقی دیود-ترانزیستور (DTL) میتوانند با یک ترانزیستور NPN با ورودیهای امیتر متعدد جایگزین شوند؛ تا نوع دیگری از مدار منطقی به نام منطق ترانزیستور-ترانزیستور یا TTL بهصورت زیر، شکل بگیرد.

این مدار گیت NAND سادهشده، شامل یک ترانزیستور ورودی TR۱ است؛ که دارای دو (یا تعداد بیشتری) پایانهی امیتر و یک مدار ترانزیستور سوئیچینگ NPN معکوس تک مرحلهای TR۲ است.

با اتصال یک یا هردو امیتر TR۱ که نشاندهندهی ورودیهای “A” و B”” است؛ به سطح منطقی “0” (LOW)، جریان بیس TR۱ از اتصال بیس-امیتر به زمین (0 ولت) میگذرد و TR۱ اشباع میشود و پایانهی کلکتور خود را دنبال میکند.

سبب اتصال بیس TR۲ به زمین (0 ولت) شده، از این رو TR۲ “خاموش (OFF)” میشود و خروجی Q در حالت بالا (HIGH) قرار میگیرد.

هنگامیکه، ورودیهای “A” و B””، در حالت HIGH و سطح منطقی “1” قرار بگیرند، ترانزیستور ورودی TR۱ “خاموش (OFF)” میشود؛ بیس ترانزیستور سوئیچینگ TR۲ در حالت HIGH قرار گرفته و آن را “روشن (ON)” میکند؛ از اینرو، خروجی Q بهدلیل عمل سوئیچینگ ترانزیستور به حالت LOW درمیآید. چند امیتر TR۱ بهعنوان ورودی بههم متصل میشوند و بنابراین، یک تابع گیت NAND را تولید میکنند.

گیت منطقی دیجیتال امیتر مزدوج

منطق امیتر مزدوج یا بهسادگی ECL، نوع دیگری از گیت منطقی دیجیتال است؛ که از منطق ترانزیستور دوقطبی استفاده میکند؛ که در آن ترانزیستورها؛ از آنجاییکه گیت منطقی دیجیتال استاندارد TTL هستند؛ در ناحیهی اشباع عمل نمیکنند. در عوض، مدارهای ورودی و خروجی ترانزیستورهای اتصال push-pull دارای منبع تغذیهی منفی، نسبت به زمین هستند.

این امر، دارای اثر افزایشی سرعت عملکرد گیتهای منطقی امیتر مزدوج تا محدودهی گیگاهرتز، نسبت به انواع استاندارد TTL میباشد؛ اما اثر نویز در منطق ECL بزرگتر است؛ زیرا ترانزیستورهای اشباعنشده در منطقهی فعال، عمل میکنند و همراه با سیگنالهای سوئیچینگ، تقویت میشوند.

زیر خانواده ۷۴ مدارهای مجتمع

با بهبود در طراحی مدار برای درنظرگرفتن تاخیر انتشار، مصرف جریان، نیازهای fan-in و fan-out و … این نوع از فناوری ترانزیستور دو قطبی TTL، اساس زیر خانوادهی “74” از آی سیهای منطقی دیجیتال را تشکیل میدهد. برای مثال میتوان به گیت NAND دو ورودی چهارتایی “7400” یا گیت NOR دو ورودی چهارتایی “7402” و… اشاره کرد.

زیرخانوادههای آیسیهای سری 74xxx مربوط به فناوریهای مختلف مورداستفاده برای ساخت گیتها هستند و با حروف بین عدد 74 و شمارهی قطعه مشخص میشوند. تعدادی از زیرخانوادههای TTL که موجود میباشند؛ طیف گستردهای از سرعت سوئیچینگ و مصرف توان را ارائه میدهند؛ مانند گیت NAND سری 74L۰۰ یا ۷۴ALS00، که “L” مخفف TTL” کمتوان” و ALS”” مخفف برای TTL” شاتکی کمتوان پیشرفته” است و این موارد در زیر ذکر شدهاست.

- 74xx یا 74Nxx: TTL استاندارد- این قطعات، خانوادهی اصلی گیتهای منطقی TTL هستند؛ که در اوایل دههی 70 معرفی شدند. دارای تاخیر انتشار آنها حدود 10 ثانیه، مصرف توان حدود 10 میلیوات و محدودهی ولتاژ تغذیه از 4.75 تا 5.25 ولت میباشند.

- 74Lxx: TTL کمتوان- مصرف توان آن، نسبت به انواع استاندارد، با افزایش تعداد مقاومتهای داخلی بهبود یافته؛ اما سرعت سوئچینگ آن، کم شدهاست. محدودهی ولتاژ تغذیه از ۴.۷۵ تا ۵.۲۵ ولت میباشد.

- 74Hxx: TTL سرعت بالا- سرعت سوئیچینگ با کاهش مقاومتهای داخلی افزایش یافته است. در این نوع مصرف توان، با افزایش همراه بودهاست. محدودهی ولتاژ تغذیه از ۴.۷۵ تا ۵.۲۵ ولت میباشد.

- 74Sxx: TTL شاتکی– فناوری شاتکی برای بهبود امپدانس ورودی، سرعت سوئیچینگ و مصرف توان (2 میلیوات) در مقایسه با انواع 74Lxx و 74xx استفاده میشود. محدودهی ولتاژ تغذیه از 4.75 تا 5.25 ولت میباشد.

- 74LSxx: TTL شاتکی کمتوان- همانند سری 74Sxx است؛ اما با افزایش مقاومتهای داخلی، مصرف توان آن بهبود یافته است. محدودهی ولتاژ تغذیه از 4.75 تا 5.25 ولت میباشد.

- 74ASxx: TTL شاتکی پیشرفته- این طراحی، بهبودیافته برای نوع شاتکی 74Sxx و بهینهشده برای افزایش سرعت سوئیچینگ با هزینهی مصرف توان حدود 22 میلیوات است. محدودهی ولتاژ تغذیه از 4.5 تا 5.5 ولت میباشد.

- 74ALSxx: TTL شاتکی کمتوان پیشرفته- این طراحی دارای، مصرف توان کمتر 1 میلیوات و سرعت بیشتر سوئیچینگ 4 نانو ثانیه، درمقایسه با انواع 74Lxx است. محدودهی ولتاژ تغذیه از 4.5 تا 5.5 ولت میباشد.

- 74HCxx: CMOS سرعت بالا- فناوری CMOS و ترانزیستورها، برای کاهش مصرف توان کمتر از 1 میکرو آمپر با ورودیهای سازگار CMOS بهکار گرفته شدهاند. محدودهی ولتاژ تغذیه از 4.5 تا 5.5 ولت میباشد.

- 74HCTxx: CMOS سرعت بالا- فناوری CMOS و ترانزیستورها، برای کاهش مصرف توان کمتر از 1 میکرو آمپر، اما با افزایش تاخیر انتشار حدود 16 نانو ثانیه، بهدلیل ورودیهای سازگار TTL بهکار گرفته شدهاند. محدودهی ولتاژ تغذیه از 4.5 تا 5.5 ولت میباشد.

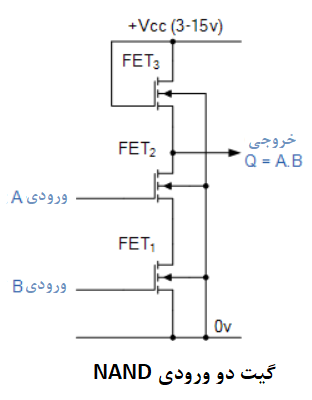

گیت منطقی دیجیتال CMOS پایه

یکی از معایب اصلی سری گیتهای منطقی دیجیتال TTL این است؛ که گیتهای منطقی آن، مبتنی بر فناوری منطق ترانزیستور دوقطبی است و از آنجاییکه، ترانزیستورها، قطعاتی هستند؛ که با جریان، عمل میکنند؛ سبب مصرف توان زیادی از یک منبع تغذیهی 5+ ولت ثابت، میشود.

همچنین، گیتهای ترانزیستور دوقطبی TTL در هنگام تغییر، از حالت “خاموش (OFF)” به “روشن (ON)” و برعکس آن، سرعت عملکرد محدودی به نام “تاخیر گیت” یا “تاخیر انتشار” دارند. برای غلبه بر این محدودیتها، MOS تکمیلی، به نام CMOS (نیمهرسانای اکسید فلز تکمیلی) گیتهای منطقی، که از “ترانزیستورهای اثر میدانی” یا FET استفاده میکنند؛ ساخته شدند.

از آنجاییکه این گیتها از هردو ماسفتهای کانال_N و کانال_P در ورودی قطعهی خود استفاده میکنند؛ در شرایط ساکن و بدون سوئچینگ، مصرف توان گیتهای CMOS تقریبا برابر با صفر (1 تا 2 میکروآمپر) است و آنها را برای استفاده در مدارهای باتری کمتوان و سرعتهای سوئچینگ تا 100 مگاهرتز و نیز برای استفاده در مدارهای زمانبندی فرکانس بالا و مدارهای کامپیوتری ایدهآل میسازد.

ن نمونه گیت اصلی CMOS، شامل ماسفت سه کانالهی_N و افزایشی بهصورت نرمالا خاموش(normally-off) است و از هرکدام از ماسفتهای FET۱ و FET۲ یک ورودی، گرفته میشود و ماسفت اضافی سوئچینگ FET۳ که بایاس شدهاست؛ دائما از طریق گیت خود “روشن(ON)” میشود.

هنگامیکه یک یا هردو ورودی “A” و B”” به زمین متصل شده و در سطح منطقی “0” قرار بگیرد؛ ماسفت FET۱ یا FET۲ ورودی مربوطه، “خاموش (OFF)” میشود و شرایط خروجی منطقی 1(HIGH) از طریق سورس FET۳ را تولید میکنند.

تنها زمانیکه هردو ورودی “A” و B”” درحالت HIGH و سطح منطقی “1” قرار میگیرند؛ به دلیل اتصال هردو ماسفت FET۱ و FET۲، جریان از طریق ماسفت مربوطه شارش مییابد و آن را “روشن (ON)” میکند و یک حالت خروجی در Q معادل سطح منطقی “0” ایجاد میکند. بنابراین، عملکرد سوئیچینگ، نشاندهندهی یک تابع گیت NAND است.

بهبود در طراحی مدار، باتوجه به سرعت سوئیچینگ، مصرف توان کم و بهبود تاخیر انتشار منجر به توسعهی خانوادهی “CD” استاندارد CMOS 4000 از آیسیهای منطقی شده است؛ که طیف TTL را تکمیل میکند.

همانند گیتهای منطقی دیجیتال استاندارد TTL، تمام گیتها و قطعات اصلی منطقی دیجیتال در پکیج CMOS مانند CD4011، یک گیت NAND دو ورودی چهارتایی یا CD4001، یک گیت NOR دو ورودی چهارتایی، شامل تمام زیرخانواده های آنها است.

همانند منطق TTL، مدارهای MOS تکمیلی (CMOS)، از این واقعیت بهره میبرند؛ که هردو قطعهی کانال N و کانال P را میتوان باهم برروی یک ماده زیرلایه ساخت؛ تا عملکردهای منطقی مختلفی را تشکیل دهند.

یکی از معایب اصلی آیسیهای CMOS در مقایسه با انواع TTL آنها، این است؛ که بهراحتی توسط الکتریسته ساکن، آسیب میبینند. همچنین برخلاف گیتهای منطقی TTL که برروی ولتاژهای جداگانهی 5+ ولت و برای دوسطح ورودی و خروجی عمل میکنند؛ گیتهای منطقی دیجیتال CMOS با یک ولتاژ تغذیه بین 3+ و 18+ ولت کار میکنند.

زیرخانوادههای CMOS رایج عبارتند از:

- سری 4000B: CMOS استاندارد- این قطعات، خانوادهی اصلی گیتهای منطقی CMOS هستند؛ که در اوایل دههی 70 معرفی شدند. محدودهی ولتاژ تغذیه از 3 تا 18 ولت c میباشد.

- سری 74C: CMOS 5 ولت- این قطعات با قطعات TTL 5 ولتی از نظر پین، سازگار هستند؛ زیرا سوئچینگ منطقی آنها با CMOS پیادهسازی شدهاست؛ اما ورودیهای سازگار TTL دارند. محدودهی کاری ولتاژ تغذیه از 3 تا 18 ولت c میباشد.

باید توجه داشت؛ که قطعات و گیتهای منطقی CMOS ، حساس به استاتیک میباشند و از اینرو، همیشه اقدامات احتیاطی را انجام دهید. کار خود را بر روی تشکهای ضد الکتریستهی ساکن یا میزهای کار زمیندار انجام دهید؛ از مچبند ضدالکتریسیته ساکن استفاده کنید و از پکیج ضدالکتریسیته ساکن تا زمانی که لازم نباشد؛ هیچ بخشی را جدا نکنید.

در مقاله بعدی در مورد گیتهای منطقی دیجیتال، تابع منطقی دیجیتال AND را در هردو مدار منطقی TTL و CMOS ، بههمراه تعریف جبر بولی و جدول درستی آن، بررسی خواهیمکرد.

دیدگاه خود را بنویسید