ترانزیستورهای اثر میدان پیوندی که به اختصار JFET (Junction Field Effect Transistor) نامیده میشوند، یک المان نیمهرسانای تک قطبی است که دارای سه پایه بوده و با ولتاژ کنترل میشود. این نوع ترانزیستورها به ۲ گروه کانال N و کانال P تقسیم میشوند.

در مقالههای مربوط به ترانزیستورهای دو قطبی پیوندی متوجه شدیم که جریان خروجی کلکتور وابسته به جریانی است که از بیس عبور میکند. بنابراین ترانزیستورهای دو قطبی المانهایی هستند که بر اساس جریان کار میکنند و از جریانی کوچک برای تولید جریان بزرگتری استفاده میشود .

اما ترانزیستورهای FET از ولتاژی که به ورودی شان، گیت (Gate) اعمال میشود برای کنترل جریانی که از آنها میگذرد استفاده میکنند بنابراین جریان خروجی از FET وابسته به ولتاژ ورودی میباشد از آن جایی که عملکرد اینگونه ترانزیستورها وابسته به میدان الکتریکی میباشد که توسط ولتاژ ورودی گیت تولید شده ، ترانزیستورهای اثر میدان المان هایی ولتاژ محور هستند .

ترانزیستورهای اثر میدان یک المان نیمهرسانای تک قطبی است که دارای ۳ پایه میباشد و ویژگیهای تقریباً مشابهی با ترانزیستورهای دو قطبی دارد. به عنوان مثال، بازده بالا، راهاندازی سریع، قدرت و ارزانقیمت بودن از ویژگیهای مشترک بین این دو ترانزیستور است. بنابراین در خیلی از مدارات میتوان ترانزیستور FET را جایگزین BJT کرد .

یک ترانزیستور JFET تیپیکال

یک ترانزیستور JFET تیپیکال

ترانزیستورهای اثر میدان میتوانند در ابعاد کوچکتری نسبت به ترانزیستورهای دوقطبی تولید شوند، به علاوه توان مصرفی و تلفات آنها کمتر از ترانزیستورهای دو قطبی است. بنابراین ترانزیستورهای اثر میدان در ساخت مدارات مجتمع مانند قطعات منطق دیجیتال CMOS ارجحیت دارند .

بر اساس مطالبی که در گذشته بیان شد دو نوع ترانزیستور دو قطبی وجود دارد :

NPN و PNP که نام گذاری نشان دهنده ترتیب قرارگیری نیمه رساناهای نوع N و نوع P در کنار یکدیگر میباشد. ترانزیستورهای JFET نیز به دو دسته تقسیم میشوند :

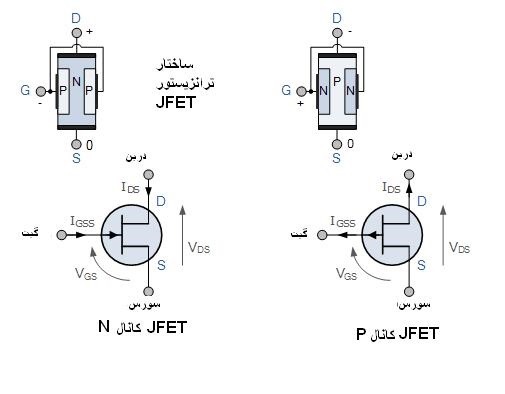

کانال N و کانال P در این ترانزیستورها جریان از مسیری که بین پایه سورس (Source) و درین (Drain) وجود دارد عبور میکند. این ترمینالها به ترتیب مشابه کلکتور و امیتر ترانزیستورهای دو قطبی عمل میکنند. مسیری که در ترانزیستورهای FET به وجود میآید و جریان از آن عبور میکند، کانال نام دارد که میتواند از نیمه رسانای نوع N یا نیمه رسانای نوع P ساخته شده باشد.

کنترل جریانی که از این کانال میگذرد ، وابسته به تغییرات ولتاژی است که به گیت اعمال میشود همانطور که از اسم آنها مشخص است، ترانزیستورهای دو قطبی به این دلیل دو قطبی نامیده میشوند که بر اساس هر دو نوع حامل ( حفره ها و الکترون ها ) کار میکنند، اما ترانزیستورهای اثر میدان یا بر اساس الکترون ها (کانال N) یا بر اساس حفره ها (کانال P) کار میکنند.

ترانزیستورهای اثر میدان دارای یک مزیت فوقالعاده بزرگ نسبت به ترانیستورهای دو قطبی هستند که این مزیت امپدانس ورودی آنها میباشد. در این ترانزیستورها امپدانس ورودی Rin فوقالعاده بالا ( چندین کیلو اهم ) میباشد، اما امپدانس ورودی BJT نسبتاً پایین است. این امپدانس ورودی بالا، ترانزیستورهای اثر میدان را نسبت به سیگنالهای ورودی ولتاژ، فوقالعاده حساس کرده. البته این مزیت یک نقطه ضعف نیز محسوب میشود، چرا که این ویژگی ترانزیستورهای FET را تبدیل به المانهایی آسیبپذیر در مقابل الکتریسیته ساکن کرده است.

ترانزیستورهای اثر میدان FET ، به دو زیر گروه گیت ایزوله شده (Insulated Gate) که ترانزیستورهای اثر میدان نیمه رسانای اکسید فلز (Oxide Semiconductor Field Effect Transistor) یا MOSFET نیز نامیده میشوند و ترانزیستورهای اثر میدان پیوندی ( Junction Field Effect Transistors) JFET تقسیم میشوند.

در بخشهای قبل مشاهده شد که ترانزیستورهای پیوندی دوقطبی ، با استفاده از دو پیوند PN ساخته شدهاند و جریان اصلی از مسیر کلکتور و امیتر میگذرد اما ترانزیستورهای اثر میدان پیوندی JFET یا JUGFET دارای یک نیمه رسانا با مقاومت بالا هستند که کانال آنها را تشکیل میدهد این کانال یا از نوع P و یا از نوع N میباشد و به حاملهای اکثریت اجازه میدهد بین دو اتصال اهمی به نام های درین و سورس جریان داشته باشند .

در ترانزیستورهای JFET کانال N ناخالصی دونور (Donor) به سیلیکون افزوده شده بنابراین جریانی که از کانال میگذرد منفی است. به این معنا که حامل ها حفره ها میباشند البته JFET کانال N نسبت به JFET کانال P هدایت بیشتری ( مقاومت کمتر ) دارد، چرا که الکترونها نسبت به حفره ها از قابلیت جابه جایی بیشتری در یک هادی برخوردار هستند و همین امر کارایی ترانزیستورJFET کانال N را نسبت به نوع کانال P آن افزایش میدهد.

همانطور که ذکر شد ۲ اتصال اهمی در دو سر کانال وجود دارد که درین و سورس نامیده میشود، علاوه بر این دو ترمینال، ترمینال دیگری به نام گیت وجود دارد که میتواند از یک نیمه رسانای نوع P یا نوع N تشکیل شده باشد که یک پیوند PN را با کانال اصلی به وجود میآورد .

روابط بین اتصالات یک ترانزیستور JFET و یک ترانزیستور BJT در زیر با یکدیگر مقایسه شده است :

مقایسه اتصالات ترانزیستورهای JFET و BJT

ترانزیستور اثر میدان FET | ترانزیستور دو قطبی BJT |

سورس (S) | << امیتر (E) |

گیت (G) | << بیس (B) |

درین (D) | << کلکتور (C) |

شکل شماتیک و ساختار پایه هر دو نوع ترانزیستور JFET در زیر نشان داده شده :

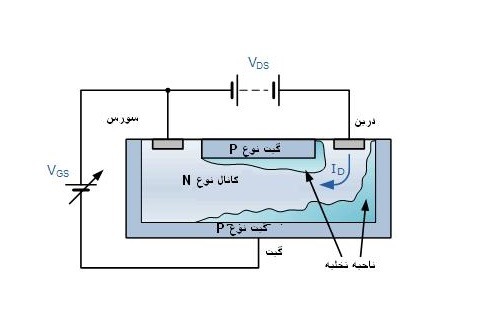

کانال نیمه رسانای ترانزیستور اثر میدان پیوندی، مسیری دارای مقاومت است که در آن یک ولتاژ VDS باعث به وجود آمدن جریان ID میشود و ترانزیستور اثر میدان پیوندی به خوبی میتواند جریان را در هر دو جهت هدایت کند. در ضمن چون کانال JFET دارای مقاومت است، عبور جریان از آن باعث ایجاد افت ولتاژ میشود و این افت ولتاژ به تدریج از درین به سورس منفی تر میشود .

در نتیجه ترانزیستورهای اثر میدان پیوندی در ترمینال درین، نقطه بایاس معکوس بالایی دارند و در ترمینال سورس، نقطه بایاس معکوس پایینتر است. بایاس معکوس باعث به وجود آمدن ناحیه تخلیه خواهد شد و پهنای ناحیه تخلیه با افزایش ولتاژ بایاس معکوس، افزایش خواهد یافت.

اندازهی جریانی که از کانال عبور میکند توسط ولتاژی که به گیت اعمال میشود قابل کنترل است که در اینجا بایاس معکوس شده است. در یک JFET کانال N ولتاژ گیت منفی است اما در JFET کانال P گیت دارای ولتاژ مثبت میباشد.

تفاوت اصلی بین JFET و BJT هنگامی نمایان میشود که پیوند JFET بایاس معکوس میشود و جریان گیت عملاً به صفر میرسد، اما در ترانزیستور BJT جریان بیس همواره وجود دارد ( حتی در حالت بایاس معکوس جریان نشتی کمی از بیس میگذرد )

بایاس کردن یک جیفت N کانال

دیاگرام بالا یک ترانزیستور کانال N را همراه گیت نوع P نشان میدهد که با قرار گرفتن در کنار کانال، یک پیوند PN را به وجود آورده و این پیوند در حالت بایاس معکوس، ناحیه تخلیه را میسازد که باعث کنترل جریان عبوری از ترانزیستور خواهد شد.

اگر ولتاژ بایاس معکوس ( گیت ) بالا برود عرض ناحیه تخلیه زیاد و عرض کانال کم میشود و با کاهش عرض کانال، مقاومت آن افزایش مییابد همانطور که میبینید ضخامت ناحیه تخلیه بین گیت و درین فوقالعاده زیاد است در حالیکه ضخامت این ناحیه بین سورس و گیت به حداقل میرسد. در ضمن اگر ولتاژ بایاس معکوس به گیت اعمال نشود عرض ناحیه تخلیه صفر خواهد بود .

در حالت (VG=0) و اعمال ولتاژی کوچک (VDS) بین درین و سورس حداکثر جریان اشباع (IDSS) از کانال از سمت درین به سورس حرکت میکند و تنها ناحیه تخلیه فوقالعاده نازکی در محل پیوندها به وجود میآید.

اگر ولتاژ منفی کمی (VGS-) به گیت اعمال شود اندازه ناحیه تخلیه به تدریخ افزایش مییابد و در نتیجه ضخامت کانال کم خواهد شد که متعاقباً باعث کاهش جریان عبوری از کانال میشود. اگر ولتاژ گیت ( بایاس معکوس) افزایش یابد هدایت کانال کاهش پیدا میکند .

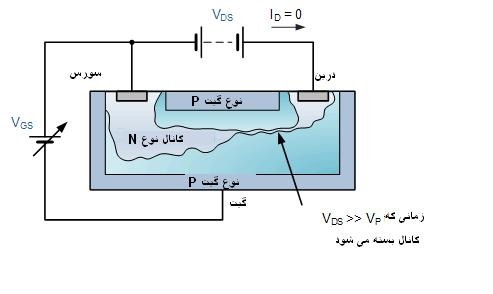

البته در حالت بایاس معکوس، جریان نشتی فوقالعاده کمی از گیت عبور میکند اگر ولتاژ VGS– خیلی زیاد باشد، عرض کانال شروع به کم شدن میکند تا جایی که هیچ جریانی از درین و سورس عبور نمیکند. در این حالت گفته میشود ترانزیستور FET قطع (Pinched-off) شده است . شبیه به ناحیه قطع (cut-off) در یک ترانزیستور BJT ،ولتاژی که با اعمال آن، کانال به طور کامل بسته میشود ولتاژ قطع (Pinch-off Voltage ) یا VP نام دارد .

کانال JFET در حالت قطع

در این ناحیه ، ولتاژ گیت (VGS ) جریان کانال را کنترل میکند و VDS تأثیر بسیار کمی در کنترل جریان دارد .

در حقیقت ترانزیستور FET همانند مقاومتی که با ولتاژ کنترل میشود عمل میکند و در حالت VGS=0t مقاومت به صفر میل میکند: همچنین اگر ولتاژ گیت فوقالعاده منفی باشد، دارای ماکزیمم مقاومت RDS=max است: در شرایط معمولی گیت JFET همواره نسبت به سورس بایاس منفی میشود .

مدل JFET

مدل JFET

فراموش نکنید ولتاژ گیت هرگز نباید مثبت باشد چرا که در این صورت تمام جریان ترانزیستور از گیت عبور میکند و باعث سوختن ترانزیستور میشود بنابراین :

ــ VGSوVDS هرگز نباید از صفر تجاوز کنند .

ــ ولتاژهای VDS و VGS با یکدیگر تفاوت دارند .

ــ ترانزیستور JFET کانال P دقیقاً همانند ترانزیستور کانال N عمل میکند با این تفاوت که :

(۱) جریان کانال به دلیل وجود حفره ها مثبت است .

(۲) پلاریته ولتاژ های بایاس در JFET کانال P برعکس پلاریته کانال N است.

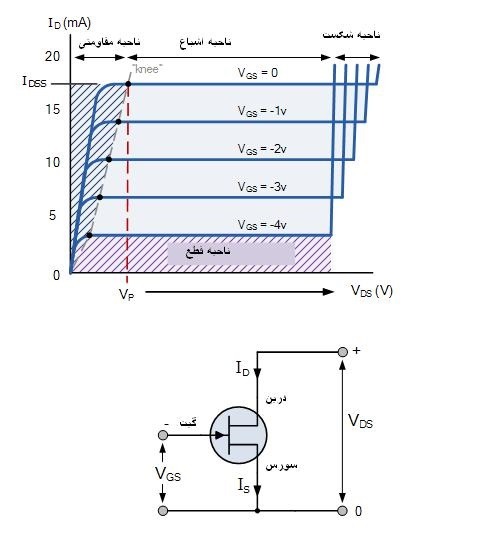

مشخصه خروجی یک ترانزیستور JFET کانال N در حالتی که گیت نسبت به سورس اتصال کوتاه شده به صورت زیر میباشد :

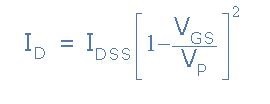

ولتاژی که به گیت اعمل میشود VGS جریانی که بین درین و سورس وجود دارد را کنترل میکند. VGSولتاژی است که بین گیت و سورس اعمال میشود و VDS ولتاژ بین درین و سورس است.

به دلیل اینکه ترانزیستور اثر میدان پیوندی توسط ولتاژ کنترل میشود ( هیچ جریانی از گیت عبور نمیکند ) جریان IS که از ترانزیستور خارج میشود برابر با جریانی است که از درین وارد ترانزیستور میشود (ID=IS )

نمونه منحنی مشخصه در شکل بالا نشان داده شد در منحنی بالا ۴ ناحیه متفاوت کاری برای ترانزیستور JFET وجود دارد که به صورت زیر است :

ناحیه اهمیک یا مقاومتی (Ohmic Region)

در این ناحیه VGS=0 بنابراین ناحیه تخلیه فوقالعاده کوچک است و JFET مانند مقاومتی که با ولتاژ کنترل میشود عمل میکند.

ناحیه قطع (Pinch-off Region)

در این ناحیه ولتاژ گیت VGS به حدی بالاست که ترانزیستور عملاً به عنوان یک کلید در حالت مدار باز عمل میکند و مقاومت کانال به بالاترین حد خود رسیده است .

ناحیه فعال یا اشباع (Active or Saturation Region)

در این ناحیه JFET هادی مناسبی است و میزان هدایت توسط ولتاژ گیت ــ سورس

(VGS) کنترل میشود اما ولتاژ درین ــ سورس (VDS) روی میزان هدایت هیچ تأثیری نخواهد داشت.

ناحیه شکست (Breakdown Region)

در این ناحیه ، ولتاژ بین درین و سورس VDS به حدی زیاد است که باعث فروپاشی کانال JFET میشود و جریان غیر قابل کنترلی از ترانزیستور عبور میکند که ممکن است سبب سوختن ترانزیستور بشود .

منحنی های مشخصه برای یک ترانزیستور JFET کانالP مشابه منحنی مشخصه کانال N میباشد با این تفاوت که جریان درین ID با افزایش مثبت ولتاژ گیت ــ سورس VGS کاهش مییابد .

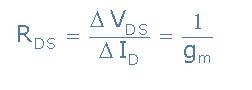

هنگامی که (VGS=VP) جریان درین ID برابر با صفر میشود ،برای عملکرد عادی VGS بین VPو صفر بایاس میشود و سپس ما میتوانیم جریان درین را برای هر نقطه بایاس در ناحیه اشباع یا فعال به صورت زیر محاسبه کنیم :

فراموش نکنید که مقدار جریان درین بین صفر ( ناحیه قطع ) و IDSS ( ماکزیمم جریان در ناحیه اشباع) خواهد بود اگر ID وVDS معلوم باشد، مقاومت کانال RDS به صورت زیر محاسبه میشود :

مقاومت کانال درین ــ سورس

gm بهره هدایت میباشد از آن جایی که JFET توسط ولتاژ کنترل میشود gm نشانگر تغییرات جریان درین نسبت به تغییرات ولتاژ گیت – سورس میباشد .

پیکربندی های مختلف ترانزیستورهای JFET

همانند ترانزیستورهای دوقطبی ، ترانزیستورهای اثر میدان نیز دارای ۳ پیکربندی متفاوت هستند که در زیر به آنها پرداخته شده :

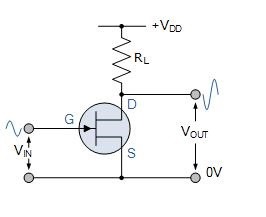

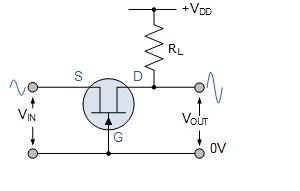

پیکربندی سورس مشترک (CS) :

در پیکربندی سورس مشترک (که به پیکربندی امیتر مشترک شباهت دارد ) ورودی به گیت اعمال میشود و خروجی مطابق شکل از درین گرفته میشود. این پیکربندی پرکاربردترین پیکربندی ترانزیستورهای FET میباشد، چرا که امپانس ورودی بالایی دارد و به خوبی ولتاژ را تقویت میکند .

از تقویت کننده های سورس مشترک معمولاً برای تقویت سیگنال های صوتی استفاده میشود در ضمن سیگنال خروجی ۱۸۰ درجه با سیگنال ورودی اختلاف فاز دارد .

پیکربندی گیت مشترک (CG) :

در پیکربندی گیت مشترک که مشابه پیکربندی بیس مشترک در ترانزیستورهای دو قطبی است، سیگنال ورودی به سورس اعمال میشود و خروجی از درین گرفته میشود. در این پیکربندی گیت به زمین متصل میشود این مدار بر خلاف مدار سورس مشترک امپدانس ورودی بالایی ندارد و در عوض امپدانس خروجی بالا میباشد .

از این نوع پیکربندی میتوان برای مدارات فرکانس بالا یا تطبیق امپدانس که امپدانس ورودی پایین باید با امپدانس خروجی بالا مطابقت داشته باشد، استفاده میشود. در این پیکربندی سیگنال خروجی با سیگنال ورودی هم فاز است.

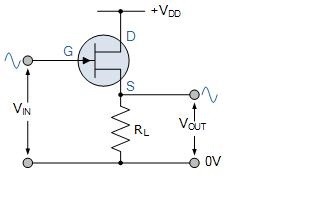

پیکربندی درین مشترک (CD) :

در پیکربندی درین مشترک که مشابه کلکتور مشترک در ترانزیستور BJT است ، سیگنال ورودی به گیت اعمال میشود و خروجی از ترمینال سورس دریافت میشود مدار درین مشترک یا دنبال کننده سورس ( Source Follower) امپدانس ورودی بالایی دارد و در مقابل امپدانس خروجی پایین میباشد. بنابراین از آن در تقویت کننده های بافر استفاده میشود.

بهره ولتاژ مدار دنبال کننده سورس کمتر از یک میباشد و سیگنال ورودی و خروجی با یکدیگر هم فاز میباشند. دلیل نام گذاری این پیکربندی به عنوان درین مشترک این است که هیچ سیگنالی به درین اعمال نمیشود و از ولتاژ درین VDD + تنها برای بایاس مدار استفاده میشود. در ضمن سیگنال خروجی مدار با سیگنال ورودی هم فاز است .

تقویت کننده JFET

ترانزیستور JFET میتواند همانند ترانزیستورهای BJT در تقویت کننده های کلاس A به کار برود. تقویت کننده کلاس A با ترانزیستور JFET از پیکربندی سورس مشترک است که مشخصه های مشابهی با تقویت کننده کلاس A امیتر مشترک BJT دارد. بزرگترین مزیت تقویت کننده های JFET نسبت به BJT امپدانس ورودی بالا میباشد که توسط ولتاژ بایاس گیت کنترل میشود .

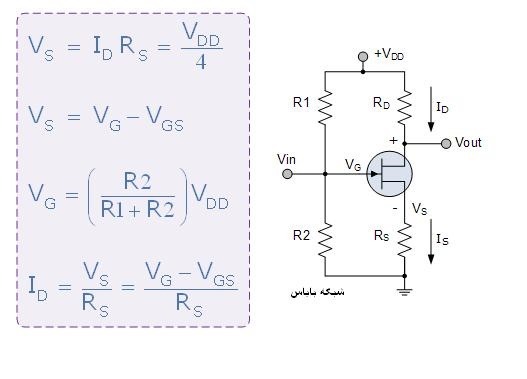

بایاس تقویت کننده JFET

مدار تقویت کننده سورس مشترک در حالت کلاس A توسط افت ولتاژی که روی دو مقاومت R1 و R2 میافتد بایاس میشود. ولتاژ در مقاومت RS معمولاً به گونهای تنظیم میشود که 1/4VDD باشد اما ضرورتی برای رعایت این اصل وجود ندارد .

ولتاژ مورد نیاز گیت برابر با صفر است (IG=0). میتوانیم ولتاژ DC مورد نیاز را با انتخاب درست مقاومتهای R1 و R2 تعیین کنیم .

کنترل جریان درین از طریق ایجاد اختلاف پتانسیل منفی در گیت، ترانزیستور اثر میدان پیوندی راتبدیل به المانی مناسب برای مدارهای سوییچینگ میکند. نباید فراموش کنید که ولتاژ گیت در یک JFET کانال N هرگز مثبت نخواهد شد چرا که در غیر این صورت جریان به جای درین از گیت عبور میکند و ترانزیستور آسیب خواهد دید. اصول راه اندازی JFET کانال P شبیه به کانال N است با این تفاوت که پلاریته ولتاژ ها برعکس میباشد .

در مقاله بعدی به گونه دیگری از ترانزیستورهای اثر میدان، به نام MOSFET میپردازیم. در ترانزیستورهای ماسفت، گیت به طور کامل از کانال حامل جریان اصلی ترانزیستور ایزوله شده است .

دیدگاه خود را بنویسید