میانگین گیر پسیو

مدارهای میانگین گیر پسیو یک ولتاژ یا سیگنال خروجی تولید میکنند که میانگین ورودیهای متعدد از یک شبکه مقاومت را نشان میدهد. در مقاله تقویتکنندههای جمع کننده دیدیم که ولتاژها یا سیگنالهای اعمال شده به ورودیهای یک مدار آپ امپ معکوس کننده را میتوان با هم «جمع» کرد تا یک خروجی واحد تولید شود و بسته به پیکربندی تقویت کننده، وارونگر یا غیر وارونگر، سیگنال خروجی جمع مثبت یا منفی تمام ورودیهای آن خواهد بود.

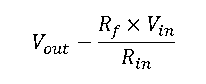

همچنین دیدیم که تقویت کننده جمع کننده هر ولتاژ ورودی را در بهره وزنی آن که با نسبت Rf/Rin، یعنی نسبت مقاومت فیدبک (Rf) به مقاومت ورودی (Rin) مربوطه تعیین میشود، ضرب میکند.

ولتاژ (یا سیگنال) خروجی جمع شده میتواند نتیجه روش جمع مستقیم باشد، که در آن مقاومتهای ورودی (Rin(1) تا Rin(n)) دارای مقادیر یکسان هستند و ولتاژ خروجی خطی مربوط به این مقادیر را تولید میکنند، یا میتواند نتیجه روش وزنی باینری باشد، که در آن مقدار هر مقاومت ورودی دو برابر میشود و یک ولتاژ خروجی پلهای تولید میکند که با «وزن» هر مقدار ورودی مطابقت دارد. تقویت کنندههای جمع کننده کاربردهای الکترونیکی بسیاری مانند طراحی میکسر صوتی یا تبدیل آنالوگ به دیجیتال (ADC) و غیره دارند.

اما علاوه بر استفاده از تقویت کنندههای عملیاتی به عنوان تقویت کننده جمع کننده (جمع) یا به عنوان تقویت کننده دیفرانسیلی (تفریق)، میتوان چندین مدار تقویت کننده عملیاتی ورودی را به عنوان مدار میانگین گیر پیکر بندی کرد که میتواند یک ولتاژ خروجی متناظر با میانگین مقادیر ولتاژ دو یا چند ورودی تولید کند.

میانگین گیر پسیو

میانگینگیر پسیو اساسا یک شبکه یا مدار مقاومتی است که طوری پیکر بندی شده است که مقدار ولتاژ خروجی آن برابر با میانگین ریاضی کل ولتاژهای ورودی است. از هر تعداد ورودی میتوان برای تشکیل یک مدار میانگین گیر، چه پسیو و چه اکتیو، استفاده کرد. مدار مقاومتی دو ورودی زیر را در نظر بگیرید.

در اینجا دو مقاومت R۱ و R۲ طوری به هم متصل شدهاند که یک سر آنها یک اتصال یا گره مشترک ایجاد میکند، در حالی که یک منبع ولتاژ به انتهای دیگر هر مقاومت اعمال شده است.

۱. مدار مقاومتی دو ورودی

۱. مدار مقاومتی دو ورودی

پس این مبنای مدار میانگین گیر پسیو است که یک ولتاژ خروجی برابر با مقدار میانگین دو ولتاژ ورودی تولید میکند، زیرا آنها عملا از طریق مقاومتها به یکدیگر متصل شدهاند. از این پیکربندی مدار اصلی میتوان برای مدارهای جمع کننده و تفریق کننده نیز استفاده کرد.

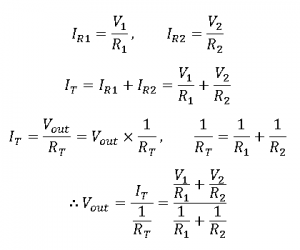

قانون جریان کیرشهف (KCL) میگوید که جمع جبری تمام جریانهای الکتریکی ورودی و خروجی از یک اتصال مدار یا گره باید برابر با صفر باشد. بنابراین مجموع جریانهای عبوری از این مدار مقاومتی پسیو برابر خواهد بود با: IT=IR1+IR2.

از این رو:

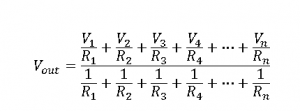

این اساسا به این معنی است که Vout برابر است با مجموع جریانهای ورودی تقسیم بر معکوس مقادیر مقاومتهای منفرد، چراکه مقاومتها عملا به طور موازی از طریق منابع ولتاژ بهم متصل شدهاند و این ایده بخشی از قضیه میلمن (Millman) است. یعنی V=I/G، که در آن «G» رسانایی است. پس همانطور که نشان داده شده، میتوانیم این معادله میانگین گیر پسیو دو ورودی پایه را برای مدارهای مقاومتی با چندین ورودی، سه، چهار یا بیشتر، گسترش دهیم.

معادله میانگین گیر پسیو

بنابراین میتوان از هر تعداد ورودی برای تولید یک مدار میانگین گیر پسیو استفاده کرد و ولتاژی که در گره مشترک دیده میشود، میانگین ریاضی ولتاژهای ورودی است.

میانگین گیر پسیو، مثال ۱

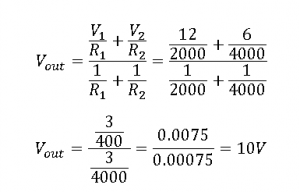

یک مدار میانگین گیر پسیو دو ورودی با استفاده از یک مقاومت 2kΩ و یک مقاومت 4kΩ ساخته شده است. اگر یک ولتاژ 12V DC به یک سر مقاومت 2kΩ و یک منبع ولتاژ 6V DC به یک سر مقاومت 4kΩ متصل باشد، ولتاژ خروجی را در محل اتصال مشترک محاسبه کنید.

ابتدا فرض کنید: R۱=2kΩ، R۲=4kΩ، V۱=12V و V۲=6V.

۲. مثال ۱- میانگین گیر پسیو

۲. مثال ۱- میانگین گیر پسیو

بنابراین ولتاژ اتصال گره مشترک 10V محاسبه شد. اما ممکن است فکر کنید: (12+6)/2=9V. ولتاژ خروجی میانگین باید 9V باشد و درست میگویید. با این حال، دو مقاومت مورد استفاده در این مثال دارای مقادیر مختلفی هستند، 2kΩ و 4kΩ، بنابراین در جریان عبوری از شبکه مقاومتی تاثیر میگذارند و چیزی تولید میکنند که به عنوان یک مدار میانگین گیر وزنی شناخته میشود. یعنی هر ورودی قبل از میانگین گیری در ضریب وزنی خود ضرب میشود.

در حقیقت برای این مثال ساده، IR1 برابر خواهد بود با: (12-10)/2000=+1mA که به گره وارد میشود و IR2 برابر خواهد بود با: (6-10)/4000=-1mA که از گره خارج میشود. یعنی 1mA جریان از منبع 12V بزرگتر به منبع تغذیه 6V کوچکتر، از طریق محل اتصال مشترک جاری میشود.

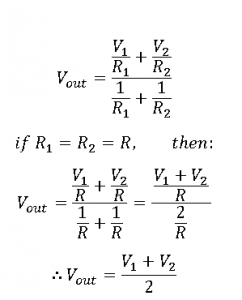

با این حال، اگر این دو مقاومت ورودی را با مقدار برابر انتخاب کنیم، به طوری که R۱=R۲=R، در این صورت جریان عبوری از محل اتصال صفر خواهد بود، زیرا دو جریان IR1 و IR2 یکسان هستند اما مقدار متضادی دارند، بنابراین همدیگر را خنثی میکنند. پس معادله میانگین گیر پسیو بالا به صورت زیر ساده میشود:

معادله میانگین گیر پسیو

یعنی با مقادیر مقاومت برابر به جای مقادیر مختلف، مقدار ولتاژ خروجی در محل اتصال مشترک دقیقا برابر با مقدار میانگین منابع ولتاژ خواهد بود و آن را به یک مدار میانگینگیر پسیو واقعی تبدیل میکند. پس با استفاده از مدار میانگین گیر ساده دو ورودی بالا، همانطور که انتظار داریم، Vout=(V۱+V۲)/2=(12+6)/2=9V.

میانگین گیر پسیو، مثال ۲

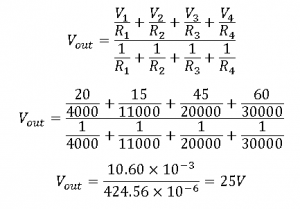

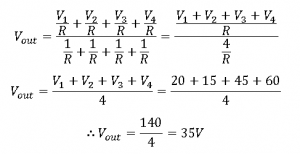

یک مدار میانگین گیر پسیو چهار ورودی با استفاده از مقادیر مقاومتی زیر ساخته شده است: R۱=4kΩ، R۲=11kΩ، R۳=20kΩ و R۴=30kΩ. اگر ولتاژهای متناظر با این مقاومتها V۱=20V، V۲=15V، V3=45V و V۴=60V باشد، ولتاژ خروجی شبکه مقاومتی پسیو را محاسبه کنید و سپس با در نظر گرفتن مقادیر برابر مقاومت، ولتاژ میانگین را به دست آورید.

۳. مثال ۲- میانگین گیر پسیو

۳. مثال ۲- میانگین گیر پسیو

با برابر بودن تمام مقادیر مقاومت و نمایش دادن آن با «R»

میبینیم که مقادیر مقاومت متصل، تاثیر زیادی در مقدار ولتاژ خروجی (Vout) دارند، چراکه مقدار میانگین وزنی 25V محاسبه شد، در حالی که میانگین ولتاژ واقعی 35V به دست آمد.

هر دو مثال که به عنوان اولین روش در اینجا گنجانده شده است، اساس قضیه میلمن را تشکیل میدهد که در آن میتوان هر تعداد شاخه مقاومت و ولتاژ موازی را به یک مقدار واحد تقلیل داد و در مثال ساده ما، چهار منبع ولتاژ، یک ولتاژ خروجی واحد 25V تولید میکنند.

مدار میانگین گیر آپ امپ

یک عیب اصلی مدار میانگین گیر پسیو بالا، این است که ولتاژ خروجی آن میتواند تحت تاثیر یک بار متصل باشد، به خصوص اگر بار امپدانس کمی داشته باشد. اما میتوانیم با افزودن تقویت کننده عملیاتی در خروجی و تبدیل آن به یک مدار میانگین گیر اکتیو، اطمینان حاصل کنیم که میانگین ولتاژ خروجی مدار میانگین گیر پسیو، درست و ثابت میماند.

سادهترین و آسانترین راه برای انجام این کار، اتصال خروجی شبکه میانگینگیر مقاومتی به ورودی یک تقویت کننده عملیاتی یا «آپ امپ» است که به عنوان «دنبال کننده ولتاژ» غیر معکوس کننده پیکربندی شده باشد. یک دنبال کننده ولتاژ در اصل یک بافر بهره واحد است که همانطور که نشان داده شده، ولتاژ خروجی مثبت تولید میکند.

مدار میانگین گیر با استفاده از دنبال کننده ولتاژ

۴.طراحی مدار میانگین گیر با دنبال کننده ولتاژ

۴.طراحی مدار میانگین گیر با دنبال کننده ولتاژ

همانطور که در آموزشهای قبلی دیدیم، امپدانس ورودی آپ امپ بسیار زیاد است، بنابراین هیچ جریانی به ترمینال ورودی غیر وارونگر وارد نمیشود. از آنجا که خروجی آپ امپ مستقیما به ورودی وارونگر آن متصل میشود، بنابراین فیدبک 100% خواهد بود، در نتیجه Vin دقیقاً برابر با Vout است که به آپ امپ یک بهره ثابت «۱» یا واحد میدهد.

یعنی Vout=Vin یک مدار میانگین گیر با خروجی مثبت تولید میکند. در اینجا مزیت این است که ورودیها عملا از یکدیگر و بار ایزوله میشوند و بنابراین میتوان از هر تعداد ورودی استفاده کرد.

میانگین گیر وارونگر

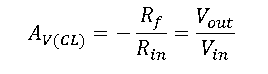

همچنین میتوان تقویت کننده عملیاتی را به عنوان تقویت کننده وارونگر پیکربندی کرد تا ولتاژ میانگین منفی در خروجی تولید کند. بهره ولتاژ حلقه بسته (AV(CL)) به دلیل مسیر فیدبک بین ترمینالهای خروجی و ورودی، به شرح زیر است:

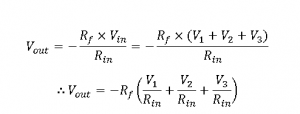

پس میتوانیم این را به شکل زیر بازنویسی کنیم:

اما برای تقویت کننده میانگین گیر، Vin=V۱+V۲+V۳+… و غیره. بنابراین اگر برای سادگی، از یک مدار میانگینگیر سه ورودی استفاده کنیم، عبارت ولتاژ خروجی به شرح زیر خواهد بود:

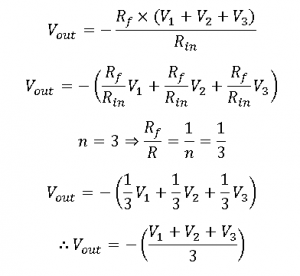

بنابراین هر ولتاژ ورودی در یک فاکتور مشترک -Rf/Rin ضرب میشود. اگر تمام مقادیر مقاومت را برابر و یکسان کنیم، یعنی Rf=Rin=”R” و تعداد ورودی برابر 3 باشد، پس Rf=Rin1=Rin2=Rin3=R و “n”=3. در نتیجه معادله بالا به شرح زیر خواهد بود:

با تنظیم بهره ولتاژ حلقه بسته تقویت کننده عملیاتی برابر با معکوس تعداد ورودیها، که در این مثال برابر 3 است، ولتاژ خروجی مدار میانگین گیر آپ امپ (Vout) و مقدار میانگین ریاضی سه ورودی جداگانه معکوس میشود.

مدار میانگین گیر معکوسکننده

۵. مدار میانگین گیر معکوس کننده

۵. مدار میانگین گیر معکوس کننده

در این مثال ساده از مدار میانگین گیر آپ امپ وارونگر، از سه ورودی استفاده کردیم. اما مدار میتواند برای استفاده از هر تعداد ورودی پیکربندی شود، به شرطی که کلیه مقاومتهای ورودی برابر با مقدار n×R تنظیم شده باشند، که در آن «R» مقدار مقاومت فیدبک، «n» تعداد کانالهای ورودی و «n×R» مقدار تمام مقاومتهای ورودی است، در غیر این صورت تقویت کننده میانگینگیر به یک تقویتکننده جمع کننده تبدیل میشود.

دیدگاه خود را بنویسید